一些ppt上的元件

组合逻辑

strobe/ST(使能脉冲):G,注意,在本例中G为低电平时,元件才有用

同上,在本例中,strobe低电平时有效(可以看到在图中,G被写成G反的形式),同时,74LS151有俩个输出(W为Y反,可以在小图中看到W和G的线上有代表反的小圈)

其他数据选择器

- strobe同样是为0有效

- 而可以看到74LS155的两个DMUX逻辑图不同,具体表现为第一种分配的是C1的反变量,而第二种分配的是C2的原变量(图中输出端皆反,而C1输入端不变,C2输入端反)

- strobe为0有效,输出0(可以理解成一个输入数据为strobe的数据分配器)

注意74LS138使能端有三个

- 两个反使能端,输出反变量

- 注意3个使能端需要为100时才能工作

- 输出的为反变量(即0)

- 可以看出分配器和译码器没有本质差别

有点小复杂(仅供观赏?)

编码器—其他信号—电信号

- 输入端有圈,故输入0表示有效

- 输出端也有圈,故输出反变量

- 注意,当没有输入信号且EI为0时(即元件被激活),EO为0,GS为1(EO输出端也有圈,故0表示有效),此特性可用于支持优先级的级联,如若有信号则输出当前信号,若无信号则由下一个级联元件决定输出信号

- 综上,GS,EO均为1时,元件未被激活;GS为1,EO为0表示元件被激活但没有输入信号;GS为0,EO为1表示元件被激活且有输入信号

利用上述性质的范例(注意用一个且门接受反变量,可类比若0表示无效,则用或门接受)

数据比较器

- 级联输入端仅有在当前元件比较结果为相同时才生效

- 有多个级联输入端有效(都为1)时,输出是UB的

奇偶校验器

时序逻辑

基本的锁存器及其特性

由卡诺图推出的状态方程(由卡诺图中的无关项可知当S,R均为1时,该方程无效)

如何推出该公式:

- 两个输出信号,Q为1的条件+Q反为0的条件

- Q为1的条件—S反为0,则与或门直接输出1

- Q反为0的条件—R反为1且Q为1

- 输入信号/元件变化时,同理类推即可

添加了一个使能信号EN减少干扰,状态方程不变

- 将门控SR锁存器中的SR信号替换成一个D信号(直接避免了不稳定的状态)

- D为1,相当于S置1,R置0;D为0,相当于S置0,R置1

- 原本的保持状态用EN信号为0控制

74LS373有个output control,当output control为0时元件有效

触发器:

- 注意上升沿触发和下降沿触发的电路图差别

- 状态转移方程等等都与普通、门控SR锁存器相同,区别在于仅仅在上升沿时有效

同上

- T表示的是是否反转

- 注意JK触发器和SR触发器的相同点、不同点(将不稳态转化成翻转操作,其余状态可直接将J类比S,K类比R)

- 注意状态方程

强置输入端

寄存器:

寄存器一般由多个D触发器组成

outputcontrol为0时输出元件有效

同上

移位寄存器()

- 将寄存数据向左或向右移位(即普通寄存器中,触发器的输出作为另一个触发器的输入)

- 当MR为0(即MR反为1时有效),通过S1,S0选择模式(平行输入,右移输入,左移输入,不变),移位时通过D来补全数据

还存在循环右移,左移的移位寄存器

计数器:

JK触发器所组成的计数器

- 一般情况下,每个触发器公用一个时钟脉冲源

- 注意分析步骤:先写出激励方程,再通过激励源写出触发器的特征方程与总输出的特征方程,通过特征方程和输出方程写出状态转移表和转移图,通过转移表和转移图得出有效状态,无效状态

自启动,非自启动电路通过状态转移图判断

JK触发器组成计数器规律

循环移位寄存器组成的二进制计数器

- k个触发器最多可计k个数

- 无法自启动

- k个触发器可计2k个数

- 无法自启动

异步计数器

中规模集成计数器

基本结构

- A,B,C,D为预置输入,当预置使能输入0时存入

- 清零字面意思,当输入0时,存储被清空为0

- 进位输出即为数字为1111时,输出1

- 计数使能使元件有效

采用上述基本结构的模13计数器

- 预置输入为0011,即从3开始数起

- Cr始终置1(即不清零)

- CO输出到LD,当产生进位时,读取预置值,使其变为0011(若连到Cr则是正常的mod16计数器)

同上

另一种改变模数方法,通过存储数字控制是否清零

通过级联多片计数器来扩大模数

- 利用了P,T不全为1时,会保持其所存储的数

- 比如0000 0000 0000—>1111 0000 0000,之后一个clk,使第二个计数器P置1,变为0000 0001 0000,之后同理,第三级同样,只有1111 1111 0000,前两个计数器都要进位时,第三级计数器才进一位

- 故mod数为16*16*16

同上,将每个计数器变成mod10计数器即可

定时脉冲产生器

时钟脉冲源电路

提供脉冲信号源

产生原始的时钟频率

将时钟脉冲进行分频

输出频率=输入频率/计数模值

同步时序逻辑分析

米里型:输出与输入,状态都有关

摩尔型:输出只与状态有关

示例:

注意:用S来统一表示各个元件的状态和

米里型转移表需要分X=0和X=1

有两个输入的情况

精简的转移表

分析电路功能:

- 写出激励方程与输出方程(通过电路图)

- 通过激励方程写出状态方程

- 写出状态转移表

- 画出状态转移图

时序逻辑设计

给定特定功能,如何设计电路:

- 确认输入和输出

- 通过问题确认状态转移图(一般直接建立一个初态)

- 化简状态转移图(归并同类项)

- 根据转移图画出转移表

- 化简转移表(归并同类项)

- 对状态进行编码(假设有k种状态,一般有两种方法:一对一法,使用k个触发器,每个触发器置1表示;计数器法,使用logk个触发器)

注意,由于判断110时,只需要注意前两个数字

故初始时一共有7个状态:1.a,表示没有任何输入;2.b和c,表示接受了一个输入为0或1;3.d,e,f,g表示接受了两个输入为00/01/10/11

通过次态确定激励D1,D2,再通过输入(即条件C)现态确定激励方程(即D1,D2何时为1)

通过现态和输入确认输出方程

若要求用JK触发器实现功能,一样是列出状态转移表,不同的是激励无法直接通过次态得到,需要对次态求解出关于现态和输入的方程,凑出JK触发器的特征(一正一反)

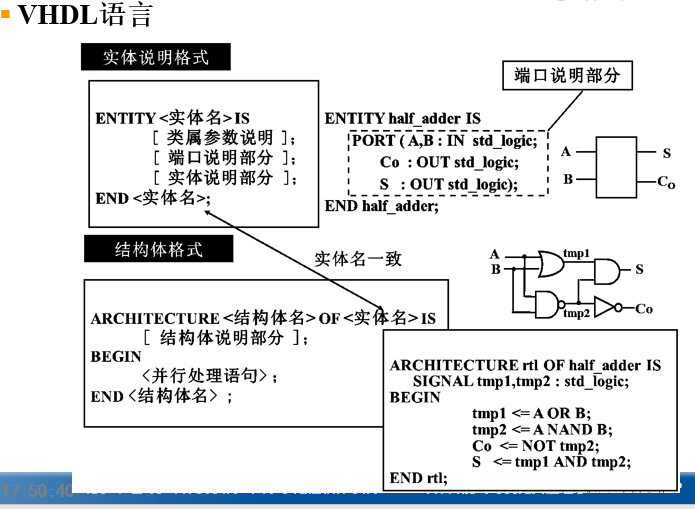

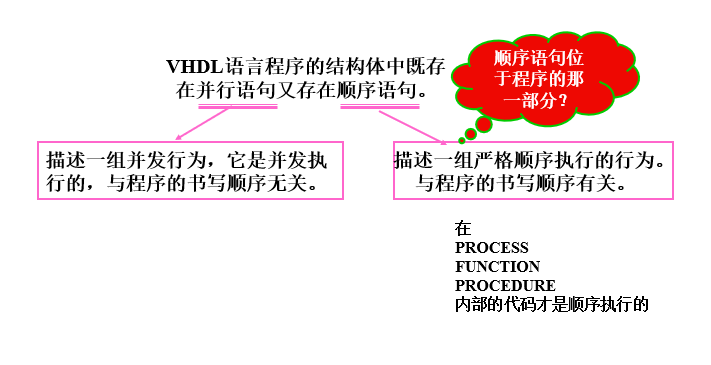

VHDL

库:存放已编译实体、结构体、程序包、配置

程序包:存放各种设计模型能共享的数据类型、常数、程序等

实体;描述所设计硬件系统的外部接口信号

结构体:描述所设计硬件系统的内部结构和功能

配置:用来从库中选取所需单元来组成新系统

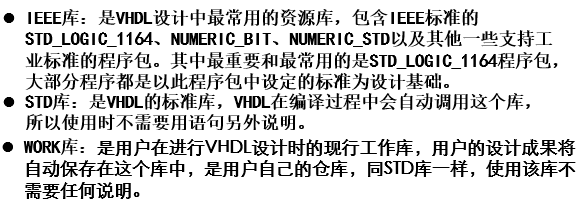

库:

库存放预先编译好的程序包,对应一个文件目录,而程序包文件就存放于目录中,所有完成的设计资源只有存入某个库中才能被其他实体共享

库的说明放在设计单元最前面,表示该库资源对以下设计单元开放,格式如下: LIBRARY 库名 ;

常用库有IEEE库、STD库和WORK库

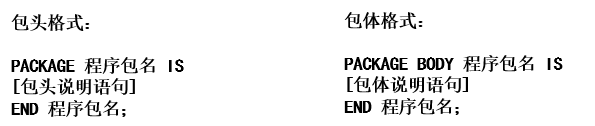

程序包:

程序包是用VHDL编写的一段程序,可以供其他设计单元调用和共享,使一组数据类型、常量和子程序被多个设计单元使用,使结构清晰(可以类比C语言里的函数)

程序包分为包头和包体两部分,均以关键词PACKAGE开头。

包头(程序包说明)是对包中使用的数据类型、元件、函数和子程序进行定义,其形式与实体定义类似。

包体规定了程序包的实际功能,存放函数和过程的程序体,允许建立内部的子程序、内部变量和数据类型。

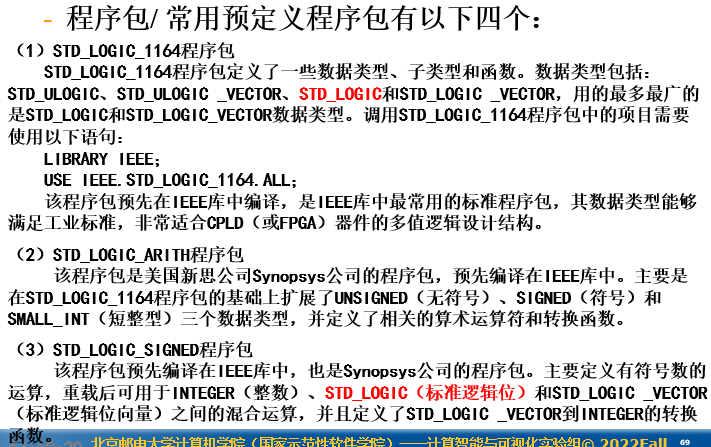

常用预定义程序包有以下四个:

实体:

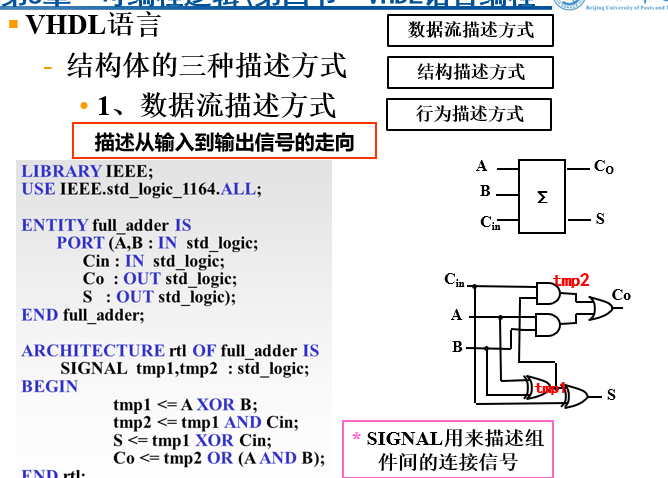

可以将实体理解为声明,结构体理解为定义?结构体中tmp1,tmp2为中间变量

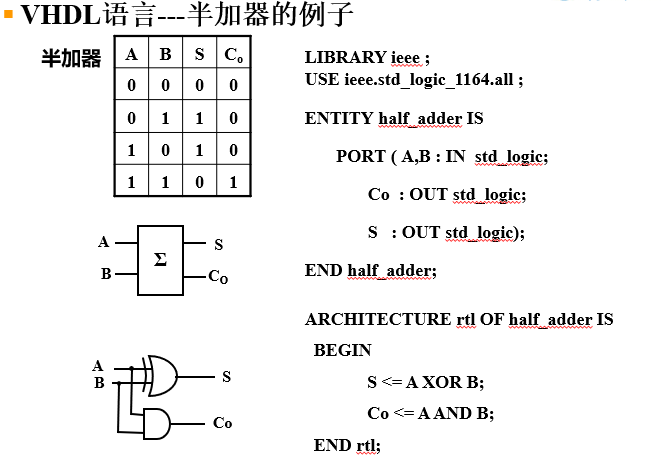

半加器例子:

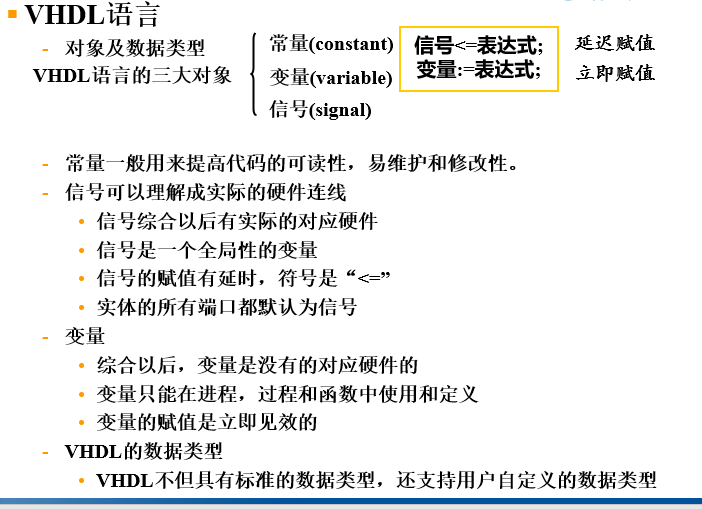

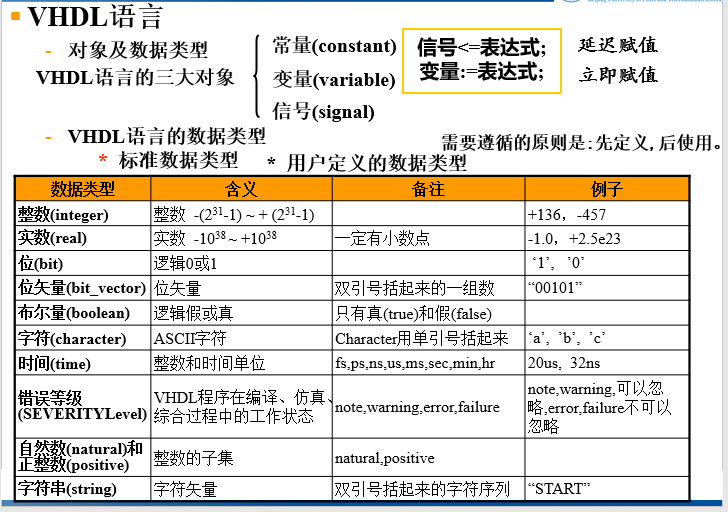

对象及数据类型:

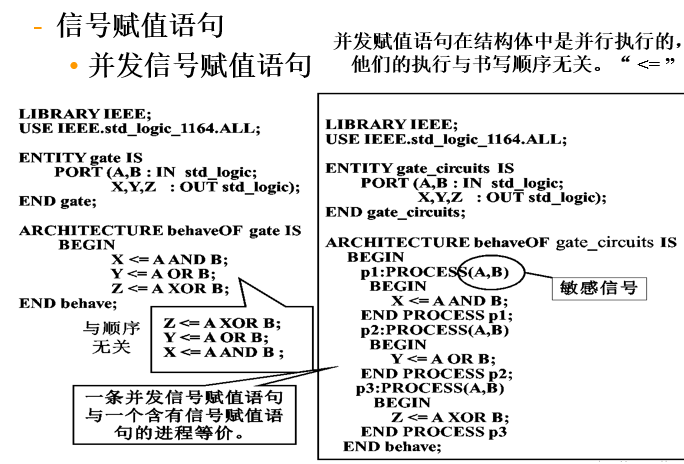

注意:信号用<=,且有延迟,变量用:=,且无延迟

变量只能在process或子进程中使用

实体端口都默认为信号(上例中的S,Co)

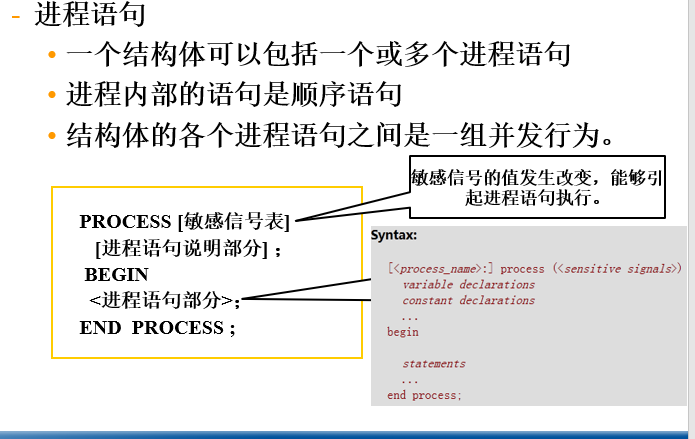

进程语句(process)

进程语句内是顺序执行,但各个顺序语句是并发的(即可以同时发生)

注意,并发信号赋值语句和信号赋值语句进程的差别

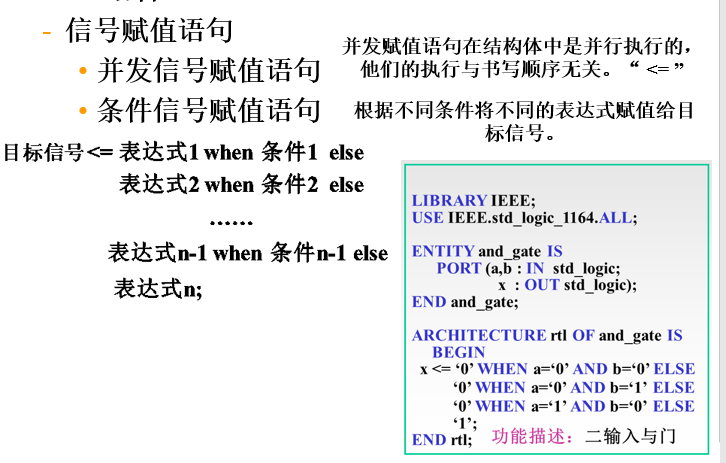

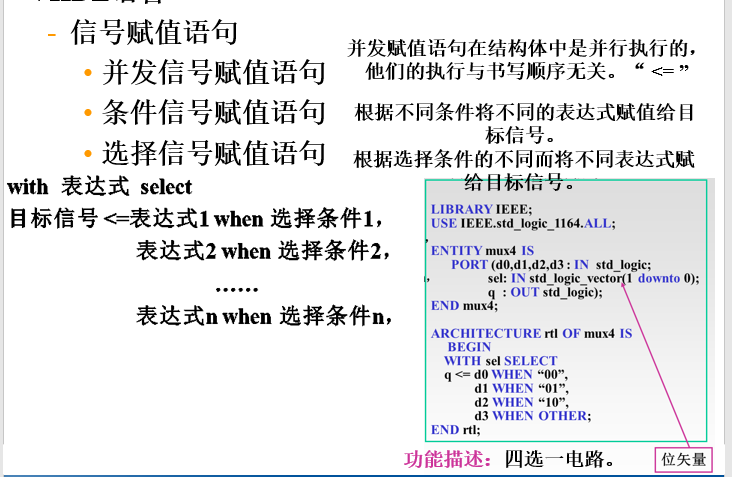

其他信号赋值语句—条件信号赋值

注意:sel为std_logic_vector,即位矢量(1 downnto 0)

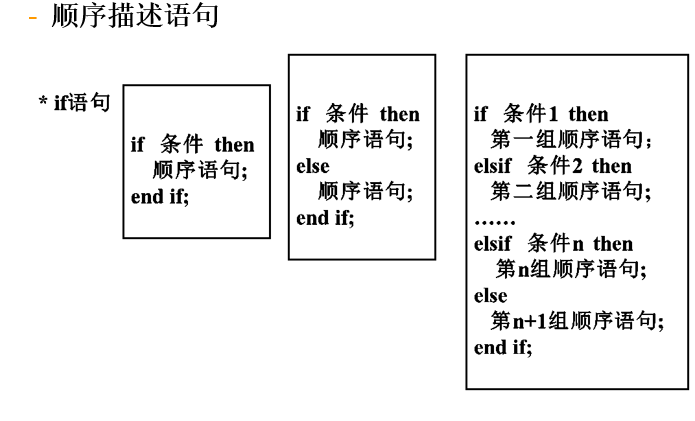

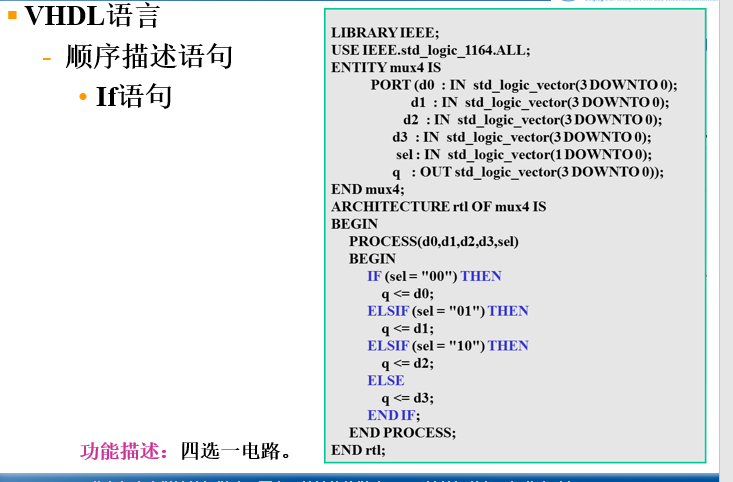

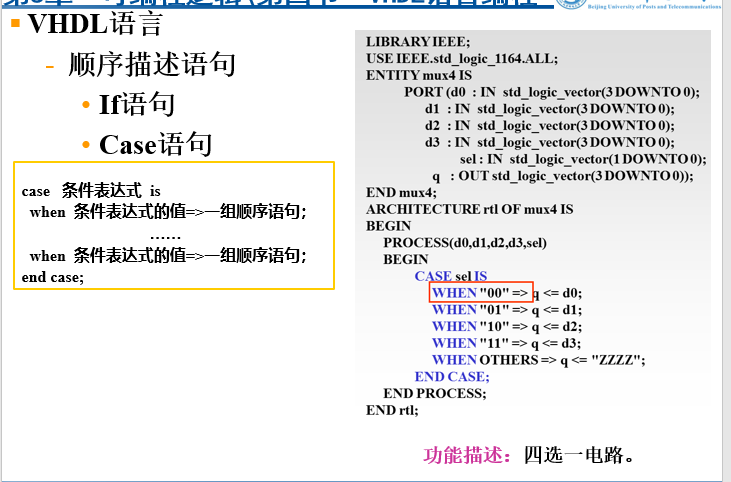

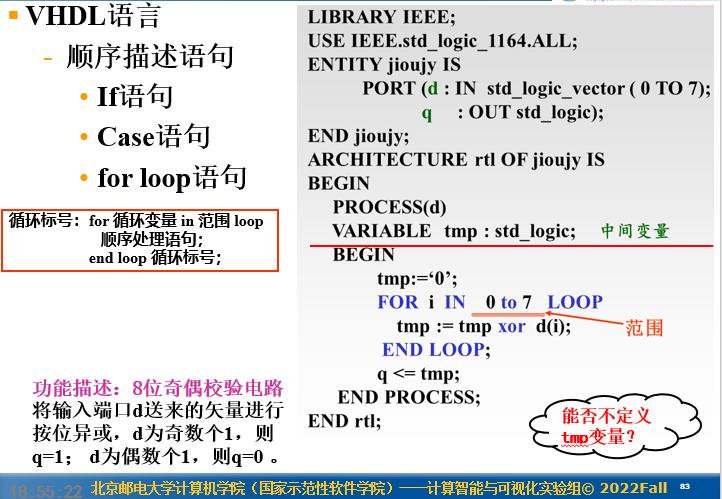

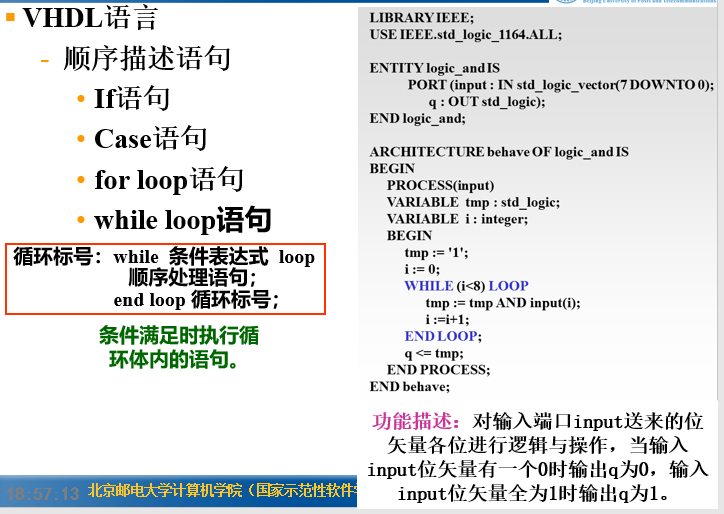

顺序描述语句

示例

注意d(0 TO 7)的写法

注意i声明为integer的变量

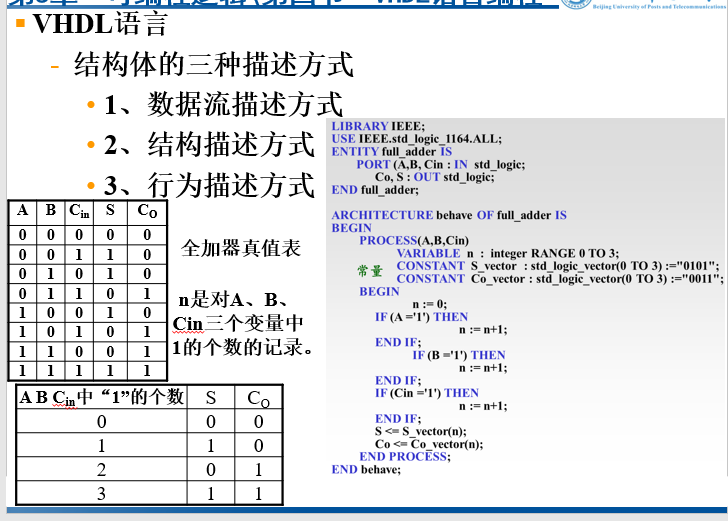

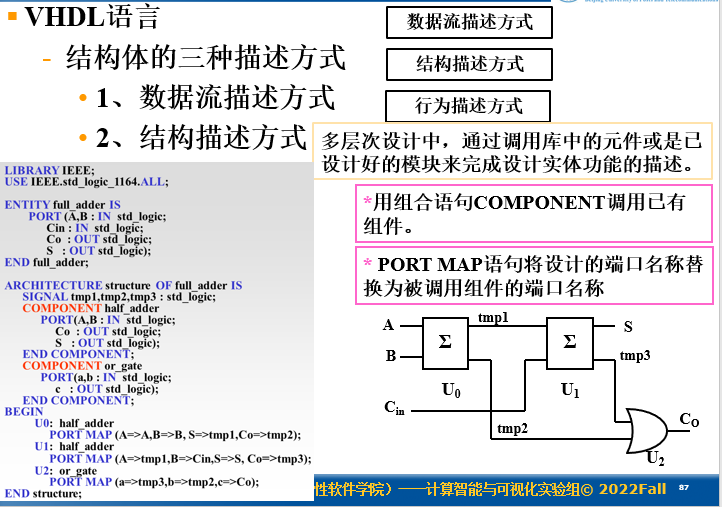

结构体的描述方式:

数据流描述方式:

重在描述信号走向

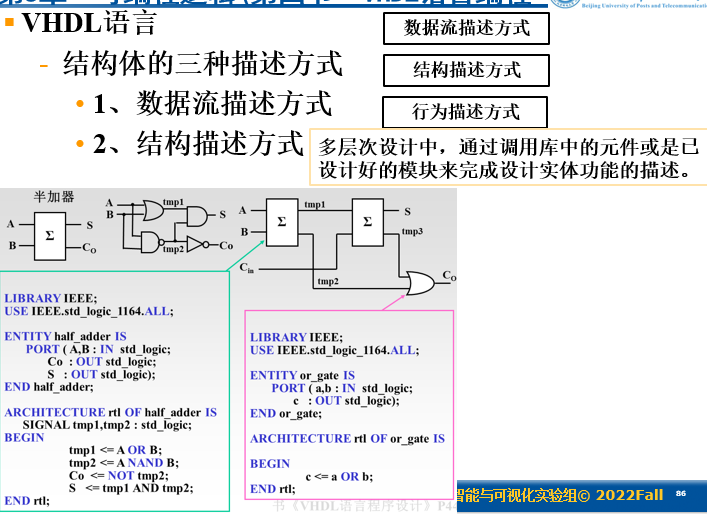

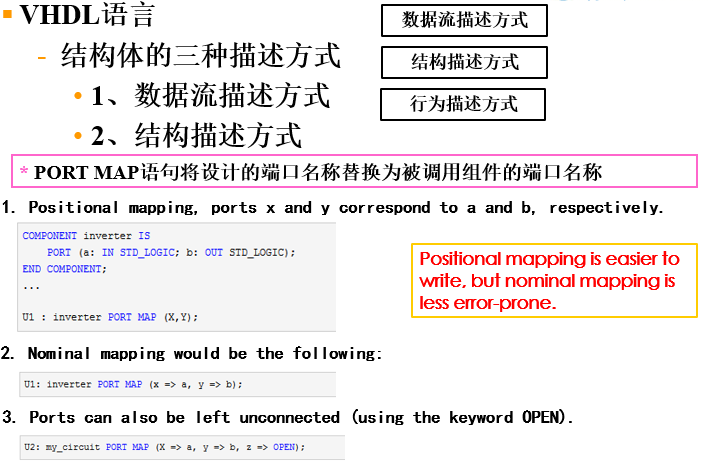

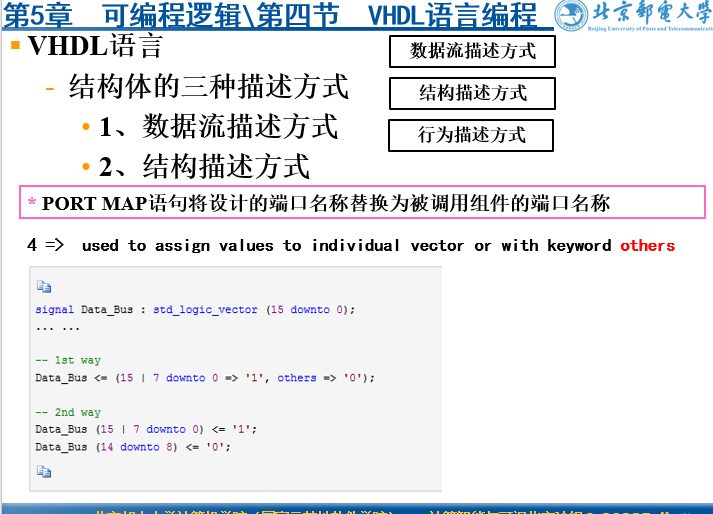

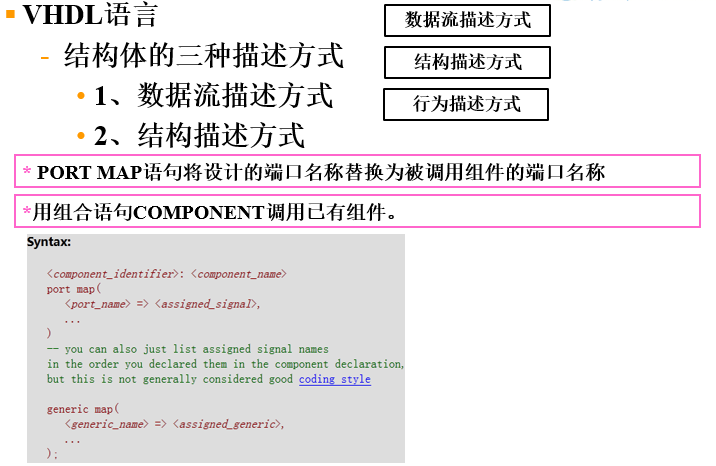

结构描述方式:

重在描述各个元件的连接关系,注意,在PORTMAP中,形参统一在前,实参统一放后

不连接的端口写OPEN

行为描述方式: